#### **USB97C223**

# Bus Powered USB 2.0 Flash Media Controller

**Datasheet**

#### **Product Features**

- Complete System Solution for interfacing SmartMedia<sup>TM</sup> (SM), Memory Stick<sup>TM</sup> (MS), High Speed Memory Stick (HSMS), Memory Stick PRO (MSPRO), Secure Digital (SD), MultiMediaCard<sup>TM</sup> (MMC), NAND Flash, Compact Flash<sup>TM</sup> (CF) and CF form-factor ATA hard drives to USB 2.0 bus

- Supports USB Bulk Only Mass Storage Compliant Bootable BIOS

- Support for simultaneous operation of all above devices. (only one at a time of each of the following groups supported: CF or ATA drive, SM or XD or NAND, SD or MMC)

- On-Chip 4-Bit High Speed Memory Stick and MS PRO Hardware Circuitry

- On-Chip firmware reads and writes High Speed Memory Stick and MS PRO

- USB Bus Power Certified

- 3.3 Volt I/O with 5V input tolerance

- Complete USB Specification 2.0 Compatibility for Bus Powered Operation

- Includes USB 2.0 Transceiver

- A Bi-directional Control and a Bi-directional Bulk Endpoint are provided.

- 8051 8 bit microprocessor

- Provides low speed control functions

- 30 Mhz execution speed at 4 cycles per instruction average

- 12K Bytes of internal SRAM for general purpose scratchpad

- 768 Bytes of internal SRAM for general purpose scratchpad or program execution while re-flashing external ROM

- Double Buffered Bulk Endpoint

- Bi-directional 512 Byte Buffer for Bulk Endpoint

- 64 Byte RX Control Endpoint Buffer

- 64 Byte TX Control Endpoint Buffer

- Internal or External Program Memory Interface

- 64K Byte Internal Code Space or Optional 64K Byte External Code Space using Flash, SRAM or EPROM memory.

- On Board 12Mhz Crystal Driver Circuit

- On-Chip 1.8V Regulator for Low Power Core Operation

- Internal PLL for 480Mhz USB2.0 Sampling, Configurable MCU clock

- Supports firmware upgrade via USB bus if "boot block" Flash program memory is used

- 15 GPIOs for special function use: LED indicators, button inputs, power control to memory devices, etc.

- Inputs capable of generating interrupts with either edge sensitivity

- Compatible with Microsoft WinXP, WinME, Win2K SP3, Apple OS10 and Linux Multi-LUN Mass Storage Class Drivers

- Win2K, Win98/98SE and Apple OS8.6 and OS9 Multi-LUN Mass Storage Class Drivers available from SMSC

- 128 Pin TQFP Package (1.0mm height, 14mm x14mm footprint)

#### ORDERING INFORMATION

Order Number(s):

USB97C223-NE for 128 pin TQFP package

© STANDARD MICROSYSTEMS CORPORATION (SMSC) 2003

80 Arkay Drive Hauppauge, NY 11788 (631) 435-6000 FAX (631) 273-3123

Standard Microsystems and SMSC are registered trademarks of Standard Microsystems Corporation. Product names and company names are the trademarks of their respective holders. Circuit diagrams utilizing SMSC products are included as a means of illustrating typical applications; consequently complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the semiconductor devices described any licenses under the patent rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT, TORT, NEGLIGENCE OF SMSC OR OTHERS, STRICT LIABILITY, BREACH OF WARRANTY, OR OTHERWISE; WHETHER OR NOT ANY REMEDY IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE; AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

# **USB97C223 Revision History**

| REVISION LEVEL<br>AND DATE | SECTION/FIGURE/ENTRY                         | CORRECTION                                                                                                                  |

|----------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Rev. 1.4                   | Cover                                        | Updated Features                                                                                                            |

| (08-27-03)                 |                                              |                                                                                                                             |

| Rev. 1.4                   | 7.2 DC Electrical Characteristics, page 17   | Updated the following parameters:                                                                                           |

| (08-27-03)                 |                                              |                                                                                                                             |

|                            |                                              | Supply Current Unconfigured, Supply Current Active (Full Speed), Supply Current Active (High Speed), Supply Current Standby |

| Rev. 1.3                   | Cover                                        | Updated features.                                                                                                           |

| (07-07-03)                 |                                              |                                                                                                                             |

| Rev. 1.3                   | Table 6.1- Pin Description, page 11          | Corrected SD-nWP from Pull-up to Pull-down.                                                                                 |

| (07-01-03)                 |                                              |                                                                                                                             |

| Rev. 1.3                   | Section 7.2 - DC Electrical Characteristics, | Added Hysteresis spec for IS buffer type.                                                                                   |

| (07-01-03)                 | page 17                                      |                                                                                                                             |

| Rev. 1.2                   | Section 3.2.1 – page 8                       | Revised ATEST, VDDP and VDDCORE                                                                                             |

| (06-06-03)                 | Table 6.1 - Pin Description – page 11        | descriptions regarding internal 1.8V regulator usage.                                                                       |

| Rev. 1.2                   | Section 3.2.1 – page 8                       | Revised second note following table.                                                                                        |

| (05-30-03)                 |                                              |                                                                                                                             |

| Rev. 1.2                   | Table 6.1 - Pin Description – page 11        | Updates to table.                                                                                                           |

| (05-30-03)                 |                                              |                                                                                                                             |

| Rev. 1.2                   | Cover page – Product Features                | 1 <sup>st</sup> bullet – changed "certifiable" to "certified.                                                               |

| (05-29-03)                 |                                              |                                                                                                                             |

| Rev. 1.2                   | Table 6.1 - page 11                          | Updated Analog Test section.                                                                                                |

| (05-28-03)                 |                                              |                                                                                                                             |

| Rev. 1.2                   | Chapter 1 - General Description - page 5     | Updated disclaimer.                                                                                                         |

| (05-28-03)                 |                                              |                                                                                                                             |

| Rev. 1.1                   | Cover page - Product Features                | Revised features.                                                                                                           |

| (04-03-03)                 |                                              |                                                                                                                             |

### **Table of Contents**

| USB97C223 I                                             | Revision History                                               | .3          |

|---------------------------------------------------------|----------------------------------------------------------------|-------------|

| Chapter 1                                               | General Description                                            | 5           |

| 2.1 Acronyn                                             | Acronyms and Definitions                                       | 6           |

| 3.1 <sup>1</sup> 128-Pin<br>3.2 128 Pin                 | Pin Table                                                      | 7<br>8      |

|                                                         | Pin Configuration                                              |             |

| Chapter 5                                               | Block Diagram1                                                 | 0           |

| 6.1 Î Pin Des<br>6.2 Buffer T                           | Pin Descriptions 1 criptions 1 ype Descriptions 1 sage Table 1 | 1<br>6      |

| 7.1 Maximu                                              | DC Parameters1 m Guaranteed Ratings1 trical Characteristics1   | 7           |

| Chapter 8                                               | Package Outline                                                | 0           |

| List of Fig                                             | gures                                                          |             |

| Figure 8.1 - 128                                        | Pin TQFP Package2                                              | 0           |

| List of Ta                                              | bles                                                           |             |

| Table 6.1 - Pin I<br>Table 6.2 - USB<br>Table 6.3 - GPI | Description                                                    | 1<br>6<br>6 |

| Table 8 1 - 128                                         | Pin TOFP Package Parameters 2                                  | n           |

Datasheet

### **Chapter 1 General Description**

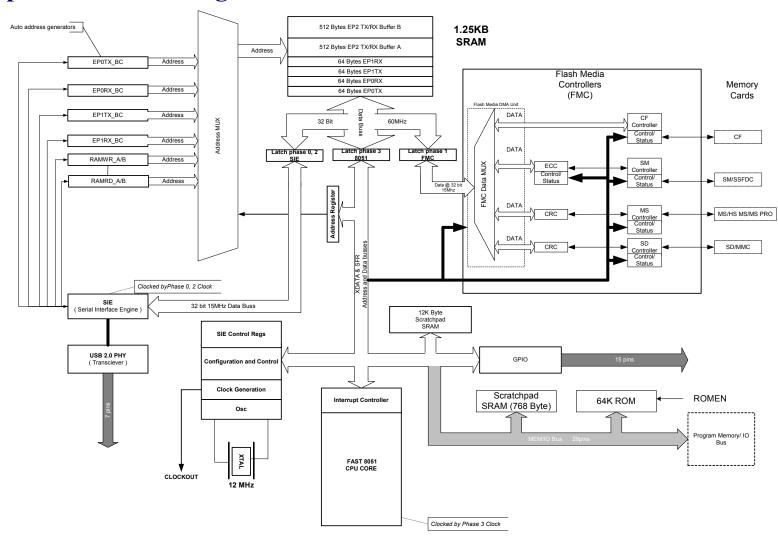

The USB97C223 is a USB2.0 Bulk Only Mass Storage Class Peripheral Controller intended for supporting CompactFlash (CF) in True IDE Mode only, SmartMedia (SM) and XD cards, Memory Stick (MS) and Memory Stick Pro (MSPRO), Secure Digital (SD) and MultiMediaCard (MMC) flash memory devices. It provides a single chip solution for the most popular flash memory cards in the market.

The device consists of a USB 2.0 PHY and SIE, buffers, Fast 8051 microprocessor with expanded scratchpad, and program SRAM, and CF, MS, SM and SD controllers. The SD controller supports both SD and MMC devices.

Provisions for external Flash Memory up to 64K bytes for program storage is provided.

12K bytes of scratchpad SRAM and 768 Bytes of program SRAM are also provided.

Fifteen GPIO pins are provided for indicators, external serial EEPROM for OEM id and system configuration information, and other special functions.

The internal ROM program is capable of implementing any combination of single or multi-LUN CF/SD/MMC/SM/MS reader functions with individual card power control and activity indication. SMSC also provides licenses\*\* for Win98 and Win2K drivers and setup utilities. Note: Please check with SMSC for precise features and capabilities for the current ROM code release.

\*Note: In order to develop, make, use, or sell readers and/or other products using or incorporating any of the SMSC devices made the subject of this document or to use related SMSC software programs, technical information and licenses under patent and other intellectual property rights from or through various persons or entities, including without limitation media standard companies, forums, and associations, and other patent holders may be required. These media standard companies, forums, and associations include without limitation the following: Sony Corporation (Memory Stick, Memory Stick Pro); SD3 LLC (Secure Digital); MultiMedia Card Association (MultiMediaCard); the SSFDC Forum (SmartMedia); the Compact Flash Association (Compact Flash); and Fuji Photo Film Co., Ltd., Olympus Optical Co., Ltd., and Toshiba Corporation (xD-Picture Card). SMSC does not make such licenses or technical information available; does not promise or represent that any such licenses or technical information will actually be obtainable from or through the various persons or entities (including the media standard companies, forums, and associations), or with respect to the terms under which they may be made available; and is not responsible for the accuracy or sufficiency of, or otherwise with respect to, any such technical information.

SMSC's obligations (if any) under the Terms of Sale Agreement, or any other agreement with any customer, or otherwise, with respect to infringement, including without limitation any obligations to defend or settle claims, to reimburse for costs, or to pay damages, shall not apply to any of the devices made the subject of this document or any software programs related to any of such devices, or to any combinations involving any of them, with respect to infringement or claimed infringement of any existing or future patents related to solid state disk or other flash memory technology or applications ("Solid State Disk Patents"). By making any purchase of any of the devices made the subject of this document, the customer represents, warrants, and agrees that it has obtained all necessary licenses under then-existing Solid State Disk Patents for the manufacture, use and sale of solid state disk and other flash memory products and that the customer will timely obtain at no cost or expense to SMSC all necessary licenses under Solid State Disk Patents; that the manufacture and testing by or for SMSC of the units of any of the devices made the subject of this document which may be sold to the customer, and any sale by SMSC of such units to the customer, are valid exercises of the customer's rights and licenses under such Solid State Disk Patents; that SMSC shall have no obligation for royalties or otherwise under any Solid State Disk Patents by reason of any such manufacture, use, or sale of such units; and that SMSC shall have no obligation for any costs or expenses related to the customer's obtaining or having obtained rights or licenses under any Solid State Disk Patents.

SMSC MAKES NO WARRANTIES, EXPRESS, IMPLIED, OR STATUTORY, IN REGARD TO INFRINGEMENT OR OTHER VIOLATION OF INTELLECTUAL PROPERTY RIGHTS. SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES AGAINST INFRINGEMENT AND THE LIKE.

No license is granted by SMSC expressly, by implication, by estoppel or otherwise, under any patent, trademark, copyright, mask work right, trade secret, or other intellectual property right.

\*\*To obtain this software program the appropriate SMSC Software License Agreement must be executed and in effect. Forms of these Software License Agreements may be obtained by contacting SMSC.

### **Chapter 2** Acronyms and Definitions

#### 2.1 Acronyms

SM: SmartMedia

SMC: SmartMedia Controller

FM: Flash Media

FMC: Flash Media Controller

**CF:** Compact Flash

CFC: CompactFlash Controller

SD: Secure Digital

SDC: Secure Digital Controller

MMC: MultiMediaCardMS: Memory Stick

MSC: Memory Stick ControllerTPC: Transport Protocol Code.ECC: Error Checking and CorrectingCRC: Cyclic Redundancy Checking

XD: XD Picture Card

#### 2.2 Definitions

**Flash Media DMA UNIT (FMDU):** The control logic in the flash media controller block as shown in the Block Diagram that support the data transfer from CFC, SMC, MSC and SDC to EP2 buffer directly.

SD/MMC: the built-in SD controller (SDC) supports both SD and MMC devices.

**Flash Media Controller Data Multiplexer (FMC DATA MUX):** The multiplexer to enable the different data path from the different flash media controllers (CFC, SMC, MSC and SDC).

# **Chapter 3** Pin Table

### 3.1 128-Pin Package

Table 3.1 - Pinout

| Table 3.1 - Pinout |                                  |                     |            |  |  |  |  |  |

|--------------------|----------------------------------|---------------------|------------|--|--|--|--|--|

|                    | CompactFlash INTERFACE (28 Pins) |                     |            |  |  |  |  |  |

| CF_D0              | CF_D1                            | CF_D2               | CF_D3      |  |  |  |  |  |

| CF_D4              | CF_D5                            | CF_D6               | CF_D7      |  |  |  |  |  |

| CF_D8              | CF_D9                            | CF_D10              | CF_D11     |  |  |  |  |  |

| CF_D12             | CF_D13                           | CF_D14              | CF_D15     |  |  |  |  |  |

| CF_nIOR            | CF_nIOW                          | CF_IRQ              | CF_nRESET  |  |  |  |  |  |

| CF_IORDY           | CF_nCS0                          | CF_nCS1             | CF_SA0     |  |  |  |  |  |

| CF_SA1             | CF_SA2                           | CF_nCD1             | CF_nCD2    |  |  |  |  |  |

|                    | SmartMedia / XD INT              | ERFACE (17 Pins)    |            |  |  |  |  |  |

| SM_D0              | SM_D1                            | SM_D2               | SM_D3      |  |  |  |  |  |

| SM_D4              | SM_D5                            | SM_D6               | SM_D7      |  |  |  |  |  |

| SM_ALE             | SM_CLE                           | SM_nRE              | SM_nWE     |  |  |  |  |  |

| SM_nWP             | SM_nB/R                          | SM_nCE              | SM_nCD     |  |  |  |  |  |

| SM_nWPS            |                                  |                     |            |  |  |  |  |  |

|                    | Memory Stick INTE                | RFACE (7 Pins)      |            |  |  |  |  |  |

| MS_BS              | MS_SDIO/MS_D0                    | MS_SCLK             | MS_INS     |  |  |  |  |  |

| MS_D1              | MS_D2                            | MS_D3               |            |  |  |  |  |  |

|                    | SD INTERFA                       | CE (7 Pins)         |            |  |  |  |  |  |

| SD_CMD             | SD_CLK                           | SD_DAT0             | SD_DAT1    |  |  |  |  |  |

| SD_DAT2            | SD_DAT3                          | SD_nWP              |            |  |  |  |  |  |

|                    | USB INTERFA                      | CE (13 Pins)        |            |  |  |  |  |  |

| USB+               | USB-                             | ATEST               | RBIAS      |  |  |  |  |  |

| VDDP               | VSSP                             | (2)VDDA             | (2)VSSA    |  |  |  |  |  |

| VREG               | XTAL1/CLKIN                      | XTAL2               |            |  |  |  |  |  |

|                    | MEMORY/IO INTER                  | RFACE (27 Pins)     |            |  |  |  |  |  |

| MA0                | MA1                              | MA2                 | MA3        |  |  |  |  |  |

| MA4                | MA5                              | MA6                 | MA7        |  |  |  |  |  |

| MA8                | MA9                              | MA10                | MA11       |  |  |  |  |  |

| MA12               | MA13                             | MA14                | MA15       |  |  |  |  |  |

| MD0                | MD1                              | MD2                 | MD3        |  |  |  |  |  |

| MD4                | MD5                              | MD6                 | MD7        |  |  |  |  |  |

| nMRD               | nMWR                             | nMCE                |            |  |  |  |  |  |

|                    | MISC (18                         | Pins)               |            |  |  |  |  |  |

| nRESET             | GPIO1                            | GPIO2               | GPIO3      |  |  |  |  |  |

| GPIO4              | GPIO5                            | GPIO6/ROMEN         | GPI07      |  |  |  |  |  |

| GPIO8              | GPIO9                            | GPIO10              | GPIO11     |  |  |  |  |  |

| GPIO12             | GPIO13                           | GPIO14              | GPIO15     |  |  |  |  |  |

| nTEST0             | nTEST1                           |                     |            |  |  |  |  |  |

|                    | DIGITAL, POWER, GRO              | OUND & NC (11 Pins) |            |  |  |  |  |  |

| (3)VDDIO           | (4)VSSIO                         | (2)VDDCORE          | (2)VSSCORE |  |  |  |  |  |

|                    | Total                            | 128                 |            |  |  |  |  |  |

| 10001120           |                                  |                     |            |  |  |  |  |  |

#### 3.2 128 Pin List Table

#### 3.2.1 128 Pin TQFP

| PIN# | NAME    | MA | PIN# | NAME    | MA | PIN# | NAME      | MA | PIN# | NAME        | MA |

|------|---------|----|------|---------|----|------|-----------|----|------|-------------|----|

| 1    | MA0     | 8  | 33   | MS_D2   | 8  | 65   | CF_nCD2   | -  | 97   | ATEST       | -  |

| 2    | MA1     | 8  | 34   | MS_D1   | 8  | 66   | CF_IRQ    | -  | 98   | VDDP        |    |

| 3    | MA2     | 8  | 35   | MS_D0   | 8  | 67   | CF_IORDY  | -  | 99   | XTAL2       | -  |

| 4    | VDDIO   |    | 36   | MS_SCLK | 8  | 68   | CF_nIOR   | 8  | 100  | XTAL1       | -  |

| 5    | MA3     | 8  | 37   | MS_BS   | 8  | 69   | CF_nIOW   | 8  | 101  | VSSP        |    |

| 6    | MA4     | 8  | 38   | SD_nWP  | ı  | 70   | CF_nRESET | 8  | 102  | VDDA(REF)   |    |

| 7    | MA5     | 8  | 39   | VDDIO   |    | 71   | CF_nCS0   | 8  | 103  | RBIAS       | -  |

| 8    | MA6     | 8  | 40   | SD_DAT0 | 8  | 72   | CF_nCS1   | 8  | 104  | VSSA(REF)   |    |

| 9    | MA7     | 8  | 41   | SD_DAT1 | 8  | 73   | CF_SA0    | 8  | 105  | VDDA        |    |

| 10   | MA8     | 8  | 42   | SD_DAT2 | 8  | 74   | VDDIO     |    | 106  | USB+        | -  |

| 11   | MA9     | 8  | 43   | SD_DAT3 | 8  | 75   | CF_SA1    | 8  | 107  | USB-        | -  |

| 12   | MA10    | 8  | 44   | SD_CMD  | 8  | 76   | CF_SA2    | 8  | 108  | VSSA        |    |

| 13   | MA11    | 8  | 45   | SD_CLK  | 8  | 77   | SM_D0     | 8  | 109  | nRESET      | -  |

| 14   | MA12    | 8  | 46   | CF_D0   | 8  | 78   | SM_D1     | 8  | 110  | VSSCORE     |    |

| 15   | MA13    | 8  | 47   | CF_D1   | 8  | 79   | VSSIO     |    | 111  | nTEST0      | -  |

| 16   | VDDCORE |    | 48   | CF_D2   | 8  | 80   | SM_D2     | 8  | 112  | nTEST1      | -  |

| 17   | MA14    | 8  | 49   | CF_D3   | 8  | 81   | SM_D3     | 8  | 113  | GPIO1       | 8  |

| 18   | MA15    | 8  | 50   | CF_D4   | 8  | 82   | SM_D4     | 8  | 114  | GPIO2       | 8  |

| 19   | MD0     | 8  | 51   | VSSIO   |    | 83   | SM_D5     | 8  | 115  | GPIO3       | 8  |

| 20   | MD1     | 8  | 52   | VSSCORE |    | 84   | SM_D6     | 8  | 116  | GPIO4       | 8  |

| 21   | MD2     | 8  | 53   | CF_D5   | 8  | 85   | SM_D7     | 8  | 117  | GPIO5       | 8  |

| 22   | MD3     | 8  | 54   | CF_D6   | 8  | 86   | SM_ALE    | 8  | 118  | GPIO6/ROMEN | 8  |

| 23   | VSSIO   |    | 55   | CF_D7   | 8  | 87   | SM_CLE    | 8  | 119  | GPIO7       | 8  |

| 24   | MD4     | 8  | 56   | CF_D8   | 8  | 88   | SM_nRE    | 8  | 120  | GPIO8       | 8  |

| 25   | MD5     | 8  | 57   | CF_D9   | 8  | 89   | SM_nWE    | 8  | 121  | GPIO9       | 8  |

| 26   | MD6     | 8  | 58   | CF_D10  | 8  | 90   | SM_nWP    | 8  | 122  | GPIO10      | 8  |

| 27   | MD7     | 8  | 59   | CF_D11  | 8  | 91   | VDDCORE   |    | 123  | GPIO11      | 8  |

| 28   | nMRD    | 8  | 60   | CF_D12  | 8  | 92   | SM_nCE    | 8  | 124  | VSSIO       |    |

| 29   | nMWR    | 8  | 61   | CF_D13  | 8  | 93   | VREG      |    | 125  | GPIO12      | 8  |

| 30   | nMCE    | 8  | 62   | CF_D14  | 8  | 94   | SM_nWPS   | -  | 126  | GPIO13      | 8  |

| 31   | MS_INS  | -  | 63   | CF_D15  | 8  | 95   | SM_nB/R   | -  | 127  | GPIO14      | 8  |

| 32   | MS_D3   | 8  | 64   | CF_nCD1 | -  | 96   | SM_nCD    | -  | 128  | GPIO15      | 8  |

**Note 1:** RBIAS is connected to the Analog Ground plane VSSA(REF) via a resistor.

Note 2: When the internal 1.8V regulator is enabled, VDDCORE (91) and VDDP(98), MUST have a 10uf +/- 20%, (equivalent series resistance (ESR) <0.1ohm) bypass capacitor to VSSA.

**Note 3:** VDDA(REF) and VSSA(REF) are same as the VDDA and VSSA respectively.

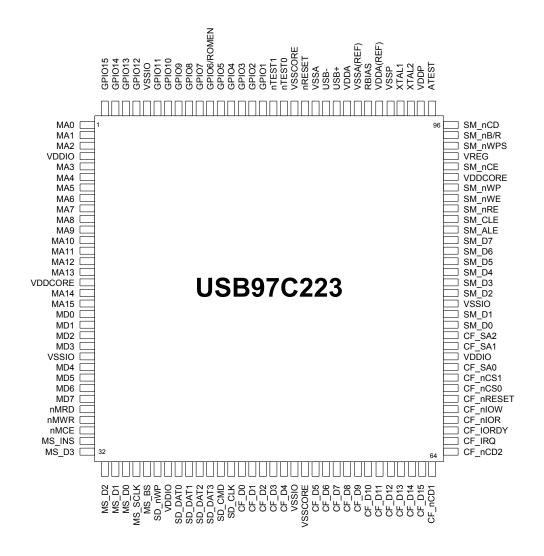

### **Chapter 4 Pin Configuration**

#### 4.1 128 Pin TQFP

# **Chapter 5** Block Diagram

### **Chapter 6 Pin Descriptions**

This section provides a detailed description of each signal. The signals are arranged in functional groups according to their associated interface.

The "n" symbol in the signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "n" is not present before the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signal. The term assert, or assertion indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation indicates that a signal is inactive.

#### 6.1 Pin Descriptions

Table 6.1 - Pin Description

| NAME                     | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                          |

|--------------------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Cor        | mpactFlash (In | True IDE mode) INTERFACE                                                                                                                             |

| CF Chip Select           | CF_nCS1    | O8             | This pin is the active low chip select 1 signal for the CF ATA device                                                                                |

| CF Chip Select<br>0      | CF_nCS0    | O8             | This pin is the active low chip select 0 signal for the task file registers of CF ATA device in the True IDE mode.                                   |

| CF Register<br>Address 2 | CF_SA2     | O8             | This pin is the register select address bit 2 for the CF device.                                                                                     |

| CF Register<br>Address 1 | CF_SA1     | O8             | This pin is the register select address bit 1 for the CF device.                                                                                     |

| CF Register<br>Address 0 | CF_SA0     | O8             | This pin is the register select address bit 0 for the CF device.                                                                                     |

| CF Interrupt             | CF_IRQ     | IPD            | This is the active high interrupt request signal from the CF device.                                                                                 |

| CF Data 15-8             | CF_D[15:8] | I/O8           | The bi-directional data signals CF_D15-CF_D8 in True IDE mode data transfer. The bi-directional data signal has an internal weak pull-down resistor. |

| CF Data7-0               | CF_D[7:0]  | 1/08           | The bi-directional data signals CF_D7-CF_D0 in the True IDE mode data transfer.                                                                      |

|                          |            |                | In the True IDE Mode, all of task file register operation occur on the CF_D[7:0], while the data transfer is on CF_D[15:0].                          |

|                          |            |                | The bi-directional data signal has an internal weak pull-down resistor.                                                                              |

| IO Ready                 | CF_IORDY   | IPU            | This pin is active high input signal from CF card.                                                                                                   |

| CF Card<br>Detection2    | CF_nCD2    | IPU            | This card detection pin is connected to the ground on the CF device, when the CF device is inserted.                                                 |

| CF Card<br>Detection1    | CF_nCD1    | IPU            | This card detection pin is connected to ground on the CF device, when the CF device is inserted.                                                     |

| NAME                       | SYMBOL            | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                          |

|----------------------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| CF Hardware<br>Reset       | CF_nRESET         | O8             | This pin is an active low hardware reset signal to CF device.                                                                                        |

| CF IO Read                 | CF_nIOR           | O8             | This pin is an active low read strobe signal for CF device, when the CFC is enabled.                                                                 |

| CF IO Write<br>Strobe      | CF_nIOW           | O8             | This pin is an active low write strobe signal for CF device, when the CFC is enabled.                                                                |

|                            |                   | Smarti         | Media INTERFACE                                                                                                                                      |

| SM Write<br>Protect        | SM_nWP            | O8             | This pin is an active low write protect signal for the SM device, when the SMC is enabled.                                                           |

| SM Address<br>Strobe       | SM_ALE            | O8             | This pin is an active high Address Latch Enable signal for the SM device, when the SMC is enabled.                                                   |

| SM Command<br>Strobe       | SM_CLE            | O8             | This pin is an active high Command Latch Enable signal for the SM device, when the SMC is enabled.                                                   |

| SM Data7-0                 | SM_D[7:0]         | I/O8           | These pins are the bi-directional data signal SM_D7-SM_D0, when the SMC is enabled.                                                                  |

| SM Read<br>Enable          | SM_nRE            | O8             | This pin is an active low read strobe signal for SM device, when SMC is enabled.                                                                     |

| SM Write<br>Enable         | SM_nWE            | O8             | This pin is an active low write strobe signal for SM device, when SMC is enabled.                                                                    |

| SM Write<br>Protect Switch | SM_nWPS           | IPU            | A write-protect seal is detected, when this pin is low.                                                                                              |

| SM Busy or<br>Data Ready   | SM_nB/R           | I              | This pin is connected to the BSY/RDY pin of the SM device.                                                                                           |

|                            |                   |                | An external pull-up resistor is required on this signal. The pull-up resistor should be attached to the power of SM/NAND flash device.               |

| SM Chip<br>Enable          | SM_nCE            | O8             | This pin is the active low chip enable signal to the SM device.                                                                                      |

| SM Card<br>Detection       | SM_nCD            | IPU            | This is the card detection signal from SM device to indicate if the device is inserted.                                                              |

|                            |                   | MEMORY         | Y STICK INTERFACE                                                                                                                                    |

| MS Bus State               | MS_BS             | 08             | This pin is connected to the BS pin of the MS device.                                                                                                |

|                            |                   |                | It is used to control the Bus States 0, 1, 2 and 3 (BS0, BS1, BS2 and BS3) of the MS device.                                                         |

| MS System<br>Data In/Out   | MS_SDIO<br>/MS_D0 | I/O8           | This pin is a bi-directional data signal for the MS device. Most significant bit (MSB) of each byte is transmitted first by either MSC or MS device. |

|                            |                   |                | The bi-directional data signal has an internal weak pull-down resistor.                                                                              |

| MS System<br>Data In/Out   | MS_D1             | IO8PD          | This pin is a bi-directional data signal for the MS device.                                                                                          |

|                            |                   |                | The bi-directional data signal has an internal weak pull-down resistor that is internally controlled.                                                |

| MS System<br>Data In/Out   | MS_D[3:2]         | I/O8           | This pin is a bi-directional data signal for the MS device.                                                                                          |

|                            |                   |                | The bi-directional data signal has an internal weak pull-down resistor.                                                                              |

| MS Card<br>Insertion       | MS_INS            | IPU            | This pin is the card detection signal from the MS device to indicate, if the device is inserted.                                                     |

| NAME                                     | SYMBOL          | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                              |  |  |  |  |

|------------------------------------------|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MS System<br>CLK                         | MS_SCLK         | O8             | This pin is an output clock signal to the MS device.                                                                                                                                                                                     |  |  |  |  |

| SD INTERFACE                             |                 |                |                                                                                                                                                                                                                                          |  |  |  |  |

| SD Data3-0                               | SD_DAT[3:0]     | I/O8           | These are bi-directional data signals.                                                                                                                                                                                                   |  |  |  |  |

| SD Clock                                 | SD_CLK          | O8             | This is an output clock signal to SD/MMC device.                                                                                                                                                                                         |  |  |  |  |

| SD Command                               | SD_CMD          | I/O8           | This is a bi-directional signal that connects to the CMD signal of SD/MMC device.                                                                                                                                                        |  |  |  |  |

| SD Write<br>Protected                    | SD_nWP          | IPD            | This pin is Write Protect Switch input signal with an internal weak pull-down.                                                                                                                                                           |  |  |  |  |

|                                          |                 | US             | B INTERFACE                                                                                                                                                                                                                              |  |  |  |  |

| USB Bus Data                             | USB-<br>USB+    | IO-U           | These pins connect to the USB bus data signals.                                                                                                                                                                                          |  |  |  |  |

| USB<br>Transceiver<br>Bias               | RBIAS           | I              | A 12.0K $\Omega$ ± 1% resistor is attached from ground to this pin to set the transceiver's internal bias currents.                                                                                                                      |  |  |  |  |

| Analog Test                              | ATEST           | IOA            | This signal is used for testing the analog section of the chip and for enabling and disabling the internal 1.8 volt regulator. This pin should be connected to VDDA to enable the internal regulator or to VSSA to disable it.           |  |  |  |  |

| 1.8v Analog<br>Power                     | VDDP            |                | 1.8v Analog Power  If the internal 1.8V regulator is enabled, this pin MUST have a 10uf +/- 20%, (equivalent series resistance (ESR) <0.10hm) bypass capacitor to VSSA. This capacitor should be placed as close to the pin as possible. |  |  |  |  |

| Analog Ground<br>Reference               | VSSP            |                | Analog Ground Reference for 1.8v Analog power.                                                                                                                                                                                           |  |  |  |  |

| 3.3v Analog<br>Power                     | VDDA            |                | 3.3v Analog Power                                                                                                                                                                                                                        |  |  |  |  |

| Analog Ground<br>Reference               | VSSA            |                | Analog Ground Reference for 3.3v Analog Power.                                                                                                                                                                                           |  |  |  |  |

| 1.8v Voltage<br>Regulator for<br>USB PHY | VREG            |                | This pin is connected to 3.3v.                                                                                                                                                                                                           |  |  |  |  |

| Crystal<br>Input/External                | XTAL1/<br>CLKIN | ICLKx          | 12Mhz Crystal or external clock input.                                                                                                                                                                                                   |  |  |  |  |

| Clock Input                              | OLIVIIV         |                | This pin can be connected to one terminal of the crystal or can be connected to an external 12Mhz clock when a crystal is not used.                                                                                                      |  |  |  |  |

| Crystal Output                           | XTAL2           | OCLKx          | 12Mhz Crystal                                                                                                                                                                                                                            |  |  |  |  |

|                                          |                 |                | This is the other terminal of the crystal, or left open when an external clock source is used to drive XTAL1/CLKIN. It may not be used to drive any external circuitry other than the crystal circuit.                                   |  |  |  |  |

|                                          |                 | MEMOI          | RY/IO INTERFACE                                                                                                                                                                                                                          |  |  |  |  |

| Memory Data<br>Bus                       | MD[7:0]         | IO8            | When using external program memory, these signals are used to transfer data between the internal CPU and the external program memory.                                                                                                    |  |  |  |  |

|                                          |                 |                | When using internal program ROM, internal weak pull up resistors are activated to prevent these pins from floating.                                                                                                                      |  |  |  |  |

| NAME                       | SYMBOL          | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                  |

|----------------------------|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory<br>Address Bus      | MA[15:0]        | O8             | These signals address memory locations within the external memory.                                                                                                                                                                                                           |

| Memory Read<br>Strobe      | nMWR            | O8             | Program Memory Write; active low                                                                                                                                                                                                                                             |

| Memory Read<br>Strobe      | nMRD            | O8             | Program Memory Read; active low                                                                                                                                                                                                                                              |

| Memory Chip<br>Enable      | nMCE            | O8             | Program Memory Chip Enable; active low. This signal is asserted, when the device is not is SUSPEND mode.                                                                                                                                                                     |

|                            |                 |                | MISC                                                                                                                                                                                                                                                                         |

| GPIO6,<br>ROMEN and<br>RXD | GPIO6<br>/ROMEN | I/O8PU         | This pin has an internal weak pullup resistor that can be enabled or disabled by the state of nRESET.  The pullup is enabled when nRESET is active.  The pullup is disabled, when the nRESET is inactive (some clock cycles later, after the rising edge of nRESET).         |

|                            |                 |                | The state of this pin is latched internally on the rising edge of nRESET to determine if internal or external program memory is used.  The state latched is stored in ROMEN bit of GPIO_IN1 register. After the rising edge of nRESET, this pin may be used as GPIO6 or RXD. |

|                            |                 |                | When pulled low via an external weak pulldown resistor, an external program memory should be connected to the memory data bus. The USB97C223 uses this external bus for program execution.                                                                                   |

|                            |                 |                | When this pin is left unconnected or pulled high by a weak pullup resistor, the USB97C223 uses the internal ROM for program execution.                                                                                                                                       |

|                            |                 |                | This pin's function while operating from internal ROM is shown in Section 6.3, GPIO Usage.                                                                                                                                                                                   |

| General<br>Purpose I/O     | GPIO1           | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                             |

|                            |                 |                | This pin's function while operating from internal ROM is shown in Section 6.3 , GPIO Usage.                                                                                                                                                                                  |

| General<br>Purpose I/O     | GPIO2           | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                             |

|                            |                 |                | This pin's function while operating from internal ROM is shown in Section 6.3, GPIO Usage.                                                                                                                                                                                   |

| General<br>Purpose I/O     | GPIO3           | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                             |

|                            |                 |                | This pin's function while operating from internal ROM is shown in Section 6.3 , GPIO Usage.                                                                                                                                                                                  |

| General<br>Purpose I/O     | GPIO4           | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                                                                             |

|                            |                 |                | This pin's function while operating from internal ROM is shown in Section 6.3 , GPIO Usage.                                                                                                                                                                                  |

| NAME                           | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                             |

|--------------------------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>Purpose I/O         | GPIO5      | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                        |

|                                |            |                | This pin's function while operating from internal ROM is shown in Section 6.3 , GPIO Usage.                                                                                                                             |

| General<br>Purpose I/O         | GPIO7      | I/O8           | This pin may be used either as input, edge sensitive interrupt input, or output.                                                                                                                                        |

|                                |            |                | This pin's function while operating from internal ROM is shown in Section 6.3 , GPIO Usage.                                                                                                                             |

| General                        | GPIO[15:8] | I/O8           | These pins may be used either as input, or output.                                                                                                                                                                      |

| Purpose I/O                    |            |                | These pins' functions while operating from internal ROM are shown in Section 6.3 , GPIO Usage.                                                                                                                          |

| RESET input                    | nRESET     | IS             | This active low signal is used by the system to reset the chip. The active low pulse should be at least $1\mu s$ wide.                                                                                                  |

| TEST Input                     | nTEST[0:1] | IPU            | These signals are used for testing the chip. User should normally tie them high externally.                                                                                                                             |

|                                | DIGIT      | TAL POWER, G   | ROUNDS, and NO CONNECTS                                                                                                                                                                                                 |

| 1.8v Digital<br>Core Power     | VDDCORE    |                | +1.8V Core power                                                                                                                                                                                                        |

|                                |            |                | All VDDCORE pins must be connected together on the circuit board.                                                                                                                                                       |

|                                |            |                | If the internal 1.8V regulator is enabled, pin 91 MUST have a 10uf +/- 20%, (equivalent series resistance (ESR) <0.10hm) bypass capacitor to VSSA, and this capacitor should be placed as close to the pin as possible. |

| 3.3v Digital I/O power         | VDDIO      |                | +3.3V I/O power                                                                                                                                                                                                         |

| VDDCORE<br>reference<br>ground | VSSCORE    |                | VDDCORE ground Reference                                                                                                                                                                                                |

| VDDIO<br>reference<br>ground   | VSSIO      |                | VDDIO ground reference                                                                                                                                                                                                  |

**Note 1:** Hot-insertion capable card connectors are required for all of flash medias. It is required for SD connector to have Write Protect switch. This allows the chip to detect MMC card.

Note 2: nMCE is normally asserted except when the system is in standby mode.

### 6.2 Buffer Type Descriptions

Table 6.2 - USB97C223 Buffer Type Descriptions

| BUFFER | DESCRIPTION                                                    |

|--------|----------------------------------------------------------------|

| I      | Input                                                          |

| IPU    | Input with controlled internal weak pull-up resistor.          |

| IPD    | Input with controlled internal weak pull-down resistor.        |

| IS     | Input with Schmitt trigger                                     |

| I/O8   | Input/Output with 8mA drive                                    |

| I/OD8  | Input/Open drain output 8mA sink                               |

| O8     | Output with 8mA drive                                          |

| I/O8PU | Input/Output with 8mA drive controlled weak pull-up resistor   |

| I/O8PD | Input/Output with 8mA drive controlled weak pull-down resistor |

| ICLKx  | XTAL clock input                                               |

| OCLKx  | XTAL clock output                                              |

| I/O-U  | Analog Input/Output Defined in USB specification               |

| O-U    | Analog Output                                                  |

| I-U    | Analog Input                                                   |

| OIA    | Special analog Input/Output                                    |

### 6.3 **GPIO Usage Table**

Table 6.3 - GPIO Usage (ROM Rev 0x00)

| NAME   | ACTIVE<br>LEVEL | SYMBOL                           | DESCRIPTION AND NOTE                                                          |

|--------|-----------------|----------------------------------|-------------------------------------------------------------------------------|

| GPIO1  | Н               | Unused                           | Unused output; NC                                                             |

| GPIO2  | Н               | EE_CS                            | Serial EE PROM chip select                                                    |

| GPIO3  | Н               | V_BUS                            | USB V bus detect                                                              |

| GPIO4  | Н               | EE_DIN/EE_DOUT                   | Serial EE PROM input/output                                                   |

| GPIO5  | Н               | HS Ind.                          | High Speed USB indicator                                                      |

| GPIO6  | Н               | A16 ( external ROM only ) /ROMEN | Int/Ext ROM select. External program memory A16 address line connect for DFU. |

| GPIO7  | Н               | EE_CLK                           | Serial EE PROM clock output                                                   |

| GPIO8  | L               | MS Power Control                 | Memory Stick Card Power Control                                               |

| GPIO9  | L               | CF Power Control                 | CompactFlash Card Power Control                                               |

| GPIO10 | L               | SM Power Control                 | SmartMedia Card Power Control                                                 |

| GPIO11 | L               | SD Power Control                 | SD/MMC Card Power Control                                                     |

| GPIO12 | Н               | MS/MSPro Activity                | Memory Stick(/Pro) Activity<br>Indicator                                      |

| GPIO13 | Н               | CF Activity                      | CompactFlash Activity Indicator                                               |

| GPIO14 | Н               | SM/XDActivity                    | SmartMedia/XD Activity Indicator                                              |

| GPIO15 | Н               | SD/MMC Activity                  | SD/MMC Activity Indicator                                                     |

### **Chapter 7 DC Parameters**

#### 7.1 Maximum Guaranteed Ratings

| Operating Temperature Range                         | 0°C to +70°C  |

|-----------------------------------------------------|---------------|

| Storage Temperature Range                           | 55° to +150°C |

| Lead Temperature Range (soldering, 10 seconds)      | +325°C        |

| Positive Voltage on any pin, with respect to Ground | 5.5V          |

| Negative Voltage on any pin, with respect to Ground | 0.3V          |

| Maximum V <sub>DD</sub> , V <sub>DDP</sub>          | +2.5V         |

| Maximum V <sub>DDIO</sub> , V <sub>DDA</sub>        | +4.0V         |

<sup>\*</sup> Stresses above the specified parameters could cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other condition above those indicated in the operation sections of this specification is not implied.

#### Notes:

- When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes on their outputs when the AC power is switched on or off. In addition, voltage transients on the AC power line may appear on the DC output. When this possibility exists, it is suggested that a clamp circuit be used.

- The name "VDD" is the same as VDDCORE

#### 7.2 DC Electrical Characteristics

$(T_A = 0^{\circ}C - 70^{\circ}C, V_{DDIO}, V_{DDA} = +3.3 V \pm 10\%, V_{DD}, V_{DDP} = +1.8 V \pm 10\%,)$

| PARAMETER            | SYMBOL            | MIN | TYP | MAX | UNITS | COMMENTS   |

|----------------------|-------------------|-----|-----|-----|-------|------------|

| I Type Input Buffer  |                   |     |     |     |       |            |

| Low Input Level      | V <sub>ILI</sub>  |     |     | 0.8 | V     | TTL Levels |

| High Input Level     | V <sub>IHI</sub>  | 2.0 |     |     | V     |            |

| IS Type Input Buffer |                   |     |     |     |       |            |

| Low Input Level      | V <sub>ILI</sub>  |     |     | 0.8 | V     | TTL Levels |

| High Input Level     | V <sub>IHI</sub>  | 2.0 |     |     | V     |            |

| Hysteresis           | V <sub>HYSI</sub> |     | 500 |     | mV    |            |

| PARAMETER              | SYMBOL            | MIN | TYP | MAX | UNITS | COMMENTS                                              |

|------------------------|-------------------|-----|-----|-----|-------|-------------------------------------------------------|

| ICLK Input Buffer      |                   |     |     |     |       |                                                       |

| Low Input Level        | V <sub>ILCK</sub> |     |     | 0.4 | V     |                                                       |

| High Input Level       | V <sub>IHCK</sub> | 2.2 |     |     | V     |                                                       |

| Input Leakage          |                   |     |     |     |       |                                                       |

| (All I and IS buffers) |                   |     |     |     |       |                                                       |

| Low Input Leakage      | I <sub>IL</sub>   | -10 |     | +10 | uA    | V <sub>IN</sub> = 0                                   |

| High Input Leakage     | I <sub>IH</sub>   | -10 |     | +10 | mA    | $V_{IN} = V_{DDIO}$                                   |

| O8 Type Buffer         |                   |     |     |     |       |                                                       |

| Low Output Level       | V <sub>OL</sub>   |     |     | 0.4 | V     | I <sub>OL</sub> = 8 mA @<br>V <sub>DDIO</sub> = 3.3V  |

| High Output Level      | V <sub>он</sub>   | 2.4 |     |     | V     | I <sub>OH</sub> = -4mA @<br>V <sub>DDIO</sub> = 3.3V  |

| Output Leakage         | l <sub>OL</sub>   | -10 |     | +10 | uA    | V <sub>IN</sub> = 0 to V <sub>DDIO</sub> (Note 7.1)   |

| I/O8 Type Buffer       |                   |     |     |     |       |                                                       |

| Low Output Level       | V <sub>OL</sub>   |     |     | 0.4 | V     | I <sub>OL</sub> = 8 mA @<br>V <sub>DDIO</sub> = 3.3V  |

| HIGH OUTPUT LEVEL      | V <sub>OH</sub>   | 2.4 |     |     | V     | I <sub>OH</sub> = -4 mA @<br>V <sub>DDIO</sub> = 3.3V |

| Output Leakage         | I <sub>OL</sub>   | -10 |     | +10 | μA    | V <sub>IN</sub> = 0 to V <sub>DDIO</sub> (Note 7.1)   |

| I/O12 Type Buffer      |                   |     |     |     |       |                                                       |

| Low Output Level       | V <sub>OL</sub>   |     |     | 0.4 | V     | I <sub>OL</sub> = 12 mA @<br>V <sub>DDIO</sub> = 3.3V |

| High Output Level      | V <sub>OH</sub>   | 2.4 |     |     | V     | I <sub>OH</sub> = -6mA @<br>V <sub>DDIO</sub> = 3.3V  |

| Output Leakage         | I <sub>OL</sub>   | -10 |     | +10 | μA    | V <sub>IN</sub> = 0 to V <sub>DDIO</sub> (Note 7.1)   |

| PARAMETER                   | SYMBOL              | MIN | TYP | MAX | UNITS | COMMENTS                                               |

|-----------------------------|---------------------|-----|-----|-----|-------|--------------------------------------------------------|

| I/O24 Type Buffer           |                     |     |     |     |       |                                                        |

| Low Output Level            | V <sub>OL</sub>     |     |     | 0.4 | V     | I <sub>OL</sub> = 24 mA @<br>V <sub>DDIO</sub> = 3.3V  |

| High Output Level           | V <sub>OH</sub>     | 2.4 |     |     | V     | I <sub>OH</sub> = -12 mA @<br>V <sub>DDIO</sub> = 3.3V |

| Output Leakage              | I <sub>OL</sub>     | -10 |     | +10 | μA    | V <sub>IN</sub> = 0 to V <sub>DDIO</sub> (Note 7.1)    |

| IO-U                        |                     |     |     |     |       |                                                        |

| (Note 7.2)                  |                     |     |     |     |       |                                                        |

| Supply Current Unconfigured | I <sub>CCINIT</sub> |     | 45  | 60  | mA    | @ $V_{DD}$ , $V_{DDP} = 1.8V$                          |

|                             |                     |     | 10  | 20  | mA    | @ V <sub>DDIO</sub> , V <sub>DDA</sub> = 3.3V          |

| Supply Current Active       | I <sub>cc</sub>     |     | 35  | 60  | mA    | $@V_{DD}V_{DDP} = 1.8V$                                |

| (Full Speed)                |                     |     | 15  | 30  | mA    | $\textcircled{Q} V_{DDIO}, V_{DDA} = 3.3V$             |

| Supply Current Active       | I <sub>CC</sub>     |     | 45  | 70  | mA    | @ $V_{DD}$ , $V_{DDP} = 1.8V$                          |

| (High Speed)                |                     |     | 15  | 30  | mA    |                                                        |

| Supply Current Standby      | I <sub>CSBY</sub>   |     | 160 | 180 | μΑ    | @ $V_{DD}$ , $V_{DDP} = 1.8V$                          |

|                             |                     |     | 215 | 240 | μA    | $ \bigcirc V_{DDIO,} V_{DDA} = $ $3.3V$                |

**Note 7.1** Output leakage is measured with the current pins in high impedance.

**Note 7.2** See Appendix A for USB DC electrical characteristics.

#### CAPACITANCE $T_A = 25^{\circ}C$ ; fc = 1MHz; $V_{DD}$ , $V_{DDP} = 1.8V$

|                         |                  | LIMITS |     |     |      |                               |

|-------------------------|------------------|--------|-----|-----|------|-------------------------------|

| PARAMETER               | SYMBOL           | MIN    | TYP | MAX | UNIT | TEST CONDITION                |

| Clock Input Capacitance | C <sub>IN</sub>  |        |     | 20  | pF   | All pins except USB           |

| Input Capacitance       | C <sub>IN</sub>  |        |     | 10  | pF   | pins (and pins                |

| Output Capacitance      | C <sub>OUT</sub> |        |     | 20  | pF   | under test tied to AC ground) |

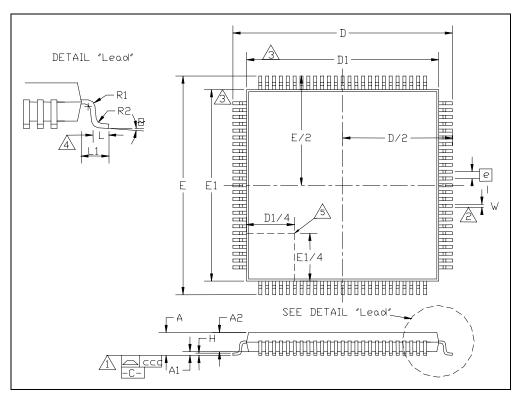

### **Chapter 8 Package Outline**

Figure 8.1 - 128 Pin TQFP Package

Table 8.1 - 128 Pin TQFP Package Parameters

|            |       |            |       | i wanaga i aramatata   |

|------------|-------|------------|-------|------------------------|

|            | MIN   | NOMINAL    | MAX   | REMARKS                |

| Α          | ~     | ~          | 1.20  | Overall Package Height |

| <b>A</b> 1 | 0.05  | ~          | 0.15  | Standoff               |

| A2         | 0.95  | ~          | 1.05  | Body Thickness         |

| D          | 15.80 | ~          | 16.20 | X Span                 |

| D1         | 13.80 | ~          | 14.20 | X body Size            |

| E          | 15.80 | ~          | 16.20 | Y Span                 |

| E1         | 13.80 | ~          | 14.20 | Y body Size            |

| Н          | 0.09  | ~          | 0.20  | Lead Frame Thickness   |

| L          | 0.45  | 0.60       | 0.75  | Lead Foot Length       |

| L1         | ~     | 1.00       | ~     | Lead Length            |

| е          |       | 0.40 Basic |       | Lead Pitch             |

| θ          | 0°    | ~          | 7°    | Lead Foot Angle        |

| W          | 0.13  | 0.18       | 0.23  | Lead Width             |

| R1         | 0.08  | ~          | ~     | Lead Shoulder Radius   |

| R2         | 0.08  | ~          | 0.20  | Lead Foot Radius       |

| ccc        | ~     | ~          | 0.08  | Coplanarity            |

#### Notes:

- 1) Controlling Unit: millimeter.

- 2) Tolerance on the true position of the leads is  $\pm$  0.035 mm maximum.

- 3) Package body dimensions D1 and E1 do not include the mold protrusion. Maximum mold protrusion is 0.25 mm.

- 4) Dimension for foot length L measured at the gauge plane 0.25 mm above the seating plane.

- 5) Details of pin 1 identifier are optional but must be located within the zone indicated.